TM 9-4935-481-14-1

C2

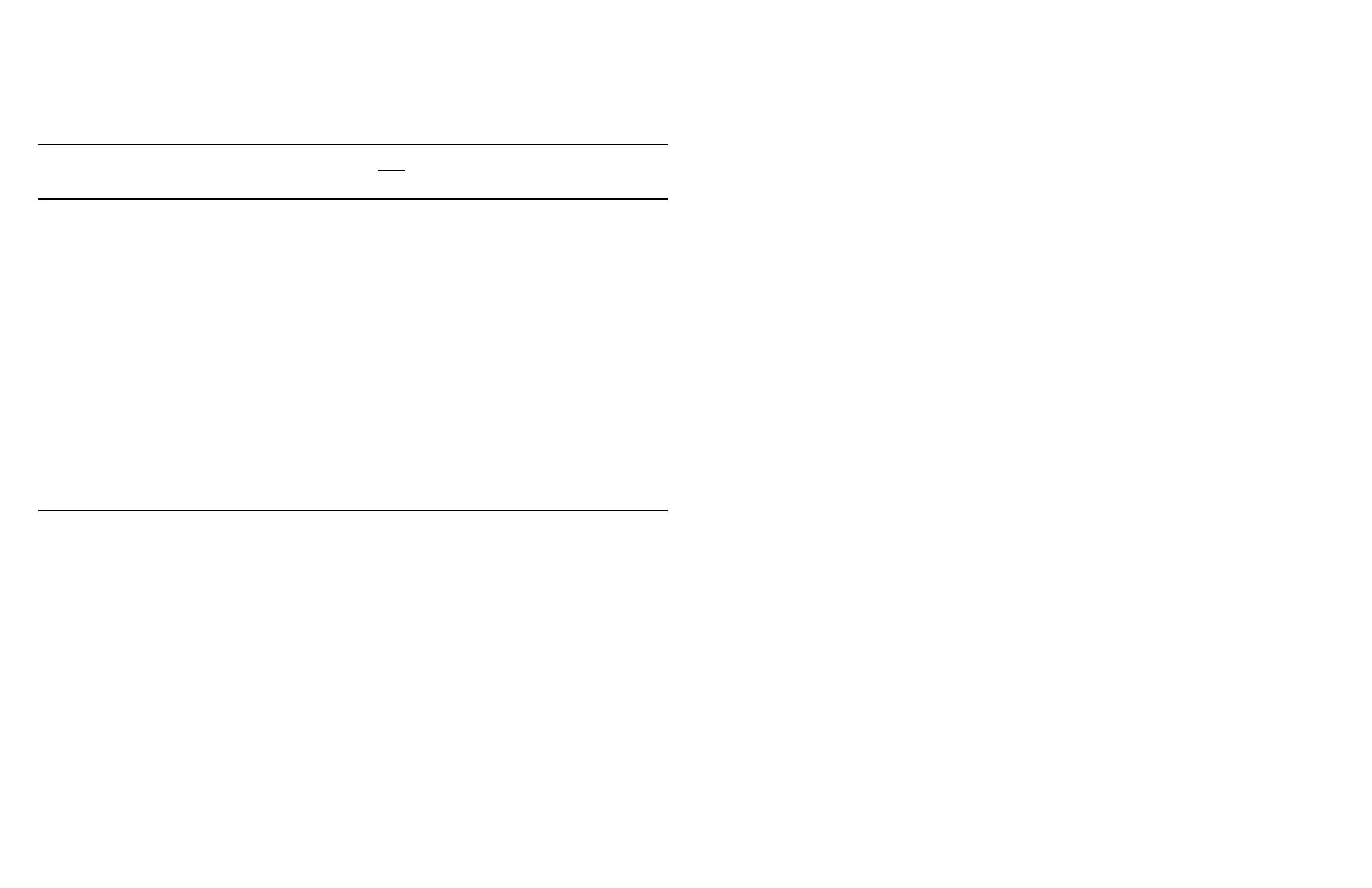

Table 3-1.3. States of Various Active Components of the

2. Generating 6V P-P, and 150 mV P-P sinewaves at any one of the following frequencies: .5 Hz, 1 Hz, 5 Hz

and 10 Hz.

Four-mode Circuit for Each Mode

3. Derating the tracker vertical and horizontal signals.

4. Providing a peak detector for a number of low frequency signals.

(c) The HIGH FREQUENCY signal is generated using a Wein bridge oscillator consisting of R1, R2, R3, R16,

Active

State

Q1, C3, C4, C7, AR1, and two 1K resistors external to the pc board. The output of the Wein bridge oscillator is applied

Component

MODE-1

MODE-2

MODE-3

MODE-4

through capacitor C8 to the half wave rectifier composed of AR2, CR1, CR2 and C11. The output of the half wave rectifier is

applied to a summing integrator. The second input to the integrator is a precision voltage opposite in polarity to the output of

the half wave rectifier. The output of the summing integrator is applied to the gate of N-type junction FET Q1 through

OV

protective diode CR3. The purpose of Q1 is to control the amount of negative feedback to amplifier AR1. When the voltage

AR5-8

(Timing not

on the gate becomes more negative, the resistance of the FET channel (between source and drain) increases, which

to scale)

increases the negative feedback to AR1. When the voltage on the gate of Q1 is made less negative, the FET channel

Z2-6

LOW

HIGH

HIGH

LOW

resistance decreases, which decreases the negative feedback to amplifier AR1. The values of the components constituting

Z1-12

HIGH

LOW

LOW

HIGH

the bridge were chosen so that the circuit is on the threshold between the non-oscillating and oscillating state when Q1 is

Q1

OFF

ON

ON

OFF

partially ON (conducting but not at its minimum resistance). Therefore, decreasing the negative feedback causes the

Q2

OFF

ON

ON

OFF

amplitude of oscillations to decrease. The amplitude of oscillations is stabilized at the value at which the output of the

AR6-7

HIGH

HIGH

SEE

HIGH

summing integrator is constant. This value is given by the formula:

NOTE 2

Vpeak = 277 (100+R6) where R6 is in K ohms

Z3-6

HIGH

HIGH

LOW

HIGH

But the value of R6 is adjustable from zero to 20K which yields 2.77V peak and 2.31V peak respectively. This shows that the

Z3-3

LOW

LOW

HIGH

LOW

amplitude of oscillations can be adjusted from 2.31V peak to 2.77V peak using trim potentiometer R6.

Q6

OFF

OFF

ON

OFF

(d) The stabilized output of the Wein bridge oscillator is applied to one input of the inverting, unity gain, summing

Q4

OFF

OFF

ON

OFF

amplifier consisting of R9, R10, R11, R12, AR4, C16 and C17. The other input to the summing amplifier is -2.5 Vdc,

AR7-7

SEE

HIGH

HIGH

HIGH

therefore, the output is:

NOTE 1

Vout = 2.5 Vdc + 2.5 sin (2pft)

Z3-8

HIGH

LOW

LOW

LOW

This output is brought out on P1-46. The stabilized output of the Wein bridge oscillator is also applied to the voltage divider

Z3-11

LOW

HIGH

HIGH

HIGH

composed of R13, R14 and R15. R14 is a trim potentiometer, which is adjusted to give 175 mV P-P signal on its output

Q7

ON

OFF

OFF

OFF

(wiper). This signal is buffered by AR5 and brought out on P1-60.

Q5

ON

OFF

OFF

OFF

Z2-11

HIGH

HIGH

HIGH

LOW

Q8

OFF

OFF

OFF

ON

Q3

OFF

OFF

OFF

ON

NOTE 1 - This output will become LOW at the end of mode-4, and will initiate mode-l. But when it becomes LOW it

sets R-S flip-flop made of two NAND gates (Z3). After this flip-flop is set the output of AR7 becomes indeterminate and

remains so until the circuit starts mode-2.

NOTE 2 - This output will become LOW at the end of mode-2, and will initiate mode-3. But when it becomes LOW it

sets R-S flip-flop made of two NAND gates (Z3). After this flip-flop is set the output of AR6 becomes indeterminate and

remains so until the start of the mode-4.

3-30.17