TM 9-4935-481-14-1

C2

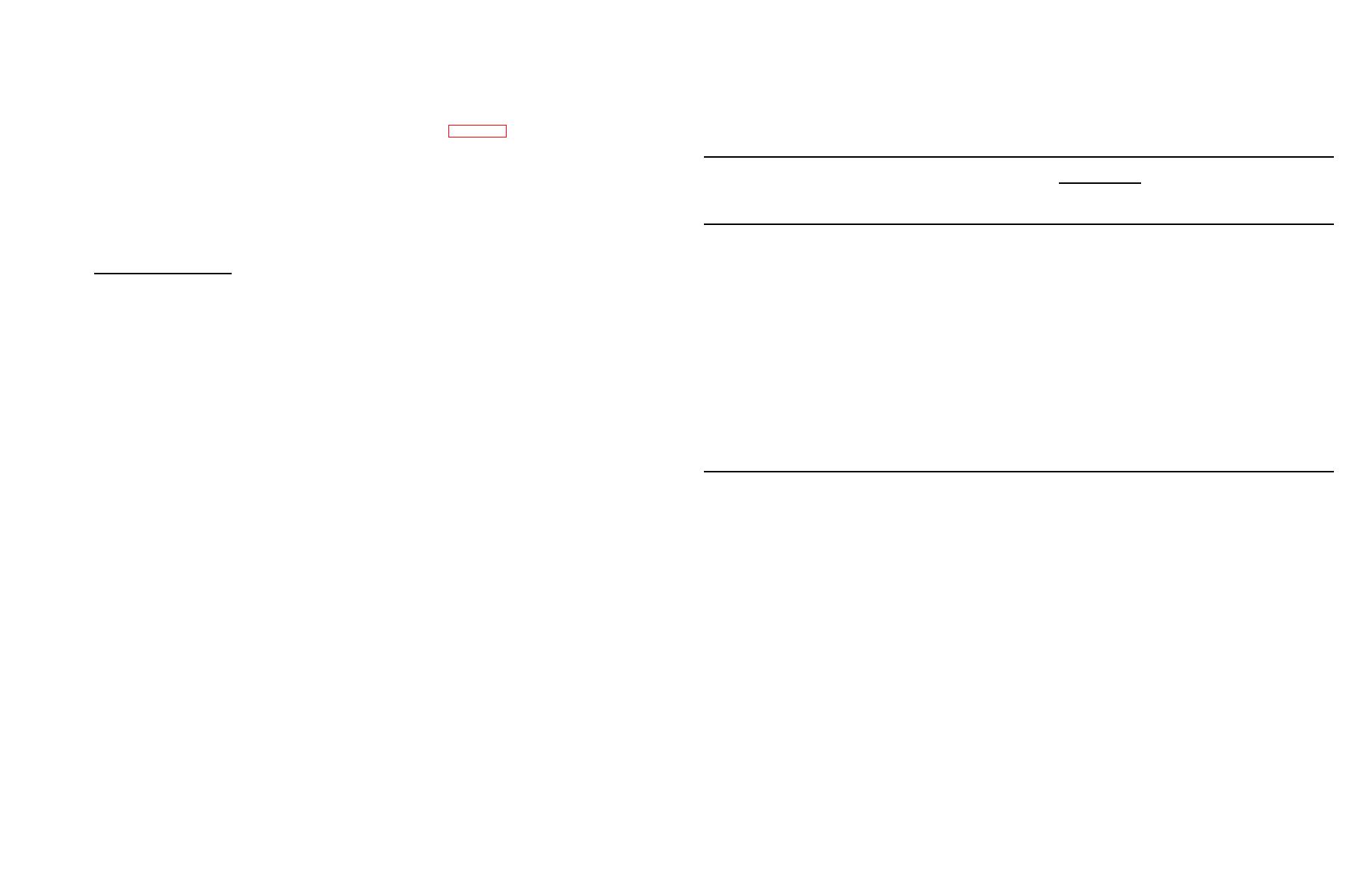

Table 3-1.1 Circuit Card A16 Control Inputs

R63 minimizes the output offset voltage of AR11.

(m) The selection of the required output(s) of the voltage dividers is accomplished by energizing appropriate

and Energized Relays Versus Output Locations

relay(s). The ON voltage required at the relay control inputs is between +1.2 Vdc and +5.5 Vdc. The control inputs and the

energized relays versus output locations and their nominal voltages are shown in table 3-1.1.

and Nominal Voltages

NOTE

Control

Energized

Selected Output

The waveforms shown in fig. 4-55 (schematic) are system

Pin on

Relay

Voltage

Location

Voltage

Location

waveforms which are applicable to the circuit performance when the

P1

(Vdc)

P1 Pin(s)

(Vdc)

P1 Pin(s)

assembly is installed in DMS-D, but which do not necessarily apply

to the circuit performance while tested in DMS-G.

80

K1

+2.50

23,51

-2.551

53

68

K2

+0.540

23,51

-0.551

53

(17) Trainer performance C A17 (fig. 4-56)

82

K3

+0.265

23,51

-0.270

53

66

K4

+0.1813

23,51

-0.1850

53

This assembly is performance tested using DMS-D, DMS-G, and test adapter A9, connector J1.

84

K5

+0.1285

23,51

-0.1311

53

(a) The circuit consists of operational amplifiers, relays, lamp drivers, and passive components. The operation of

67

K6

+0.0995

23,51

-0.1015

53

this circuit is described below:

65

K7

+0.0820

23,51

-0.0837

53

75

K8, K11 Off

+7.500

33,37

-7.653

34

(b) AR1 is a unity gain non-inverting buffer. Resistor R1 protects AR1 in case of an inadvertant short from pin 36

76

K9, K11 Off

+1.980

33,37

-2.020

34

on connector P1 to ground. Capacitor C4 and resistor R1 form a low-pass noise filter at the input to AR1. Trim

62

K10, K11 Off

+0.941

33,37

-0.9602

34

potentiometer R2 provides an offset voltage adjustment (cancellation) at the output of AR1. The output of AR1 is connected

78,75

K11, K8

+7.500

33,37

-7.653

34

to P1-35 through an 800 ohm resistor. An external load of 604 ohms is connected to P1-35, therefore the voltage at P1-35 is

78,76

K11, K9

+0.992

33,37

-1.012

34

.43 of the voltage at the output of AR1. The output of AR1 is also connected to P1-34 through a 1.2K resistor, and an

78,62

K11, K10

+0.406

33,37

-0.4143

34

external 1.4K load is connected to P1-34, therefore the voltage at P1-34 is .538 of the output voltage of AR1.

64

K12

+7.500

32

-7.653

30

(c) AR2 is a unity gain non-inverting buffer. Resistor R5 protects AR2 in case of an inadvertant short from P1-37

+4.000

28,29

to ground. Capacitor C7, and resistor R5 form a low-pass noise filter at the input to AR2. Trim potentiometer R6 provides an

61

K13

+0.992

28,29,32

-1.012

30

offset voltage adjustment (cancellation) at the output of AR2. The output of AR2 is connected to P1-37, and to P1-42, P1-40,

63

K14

+0.411

28,29,32

-0.4194

30

P1-39 and P1-38 through resistors R7 (800 ohms), R8 (1.2K), R9 (800 ohms), and R10 (1.2K) respectively. External load

resistors of 604 ohms are connected to P1-42, and to P1-39 and external load resistors of 1400 ohms are connected to P1-40

and P1-38. These resistors form four voltage dividers producing at P1-42, and P1-39 .43 of the output voltage of AR2 and

.538 of the AR2 output voltage at P1-40 and P1-38.

3-30.12