TM9-4935-481-14-1

parallel entry capability which is not used in DMS application; therefore, the parallel entry enable input PE (pin 9) is disabled

by connecting it to +5 Vdc. The counter has two count enable inputs; one at pin 7, and the other at pin 10. Both of these

inputs, and also the master reset (MR) input (pin 1) must be high to enable the clock counting mode.

(d) The first line in the truth table (fig. 3-23) corresponds to decimal zero and is obtained by applying a

momentary low to the MR input (pin 1). The counter is equipped with a terminal count (TC) output at pin 15. This output is

low except after the ninth clock pulse, when it goes high and remains high until the end (trailing edge) of the 10th clock pulse,

when it goes low. In other words, the TC output is high when counter output (Q, Q1, Q2, Q3) is equivalent to decimal 9.

0

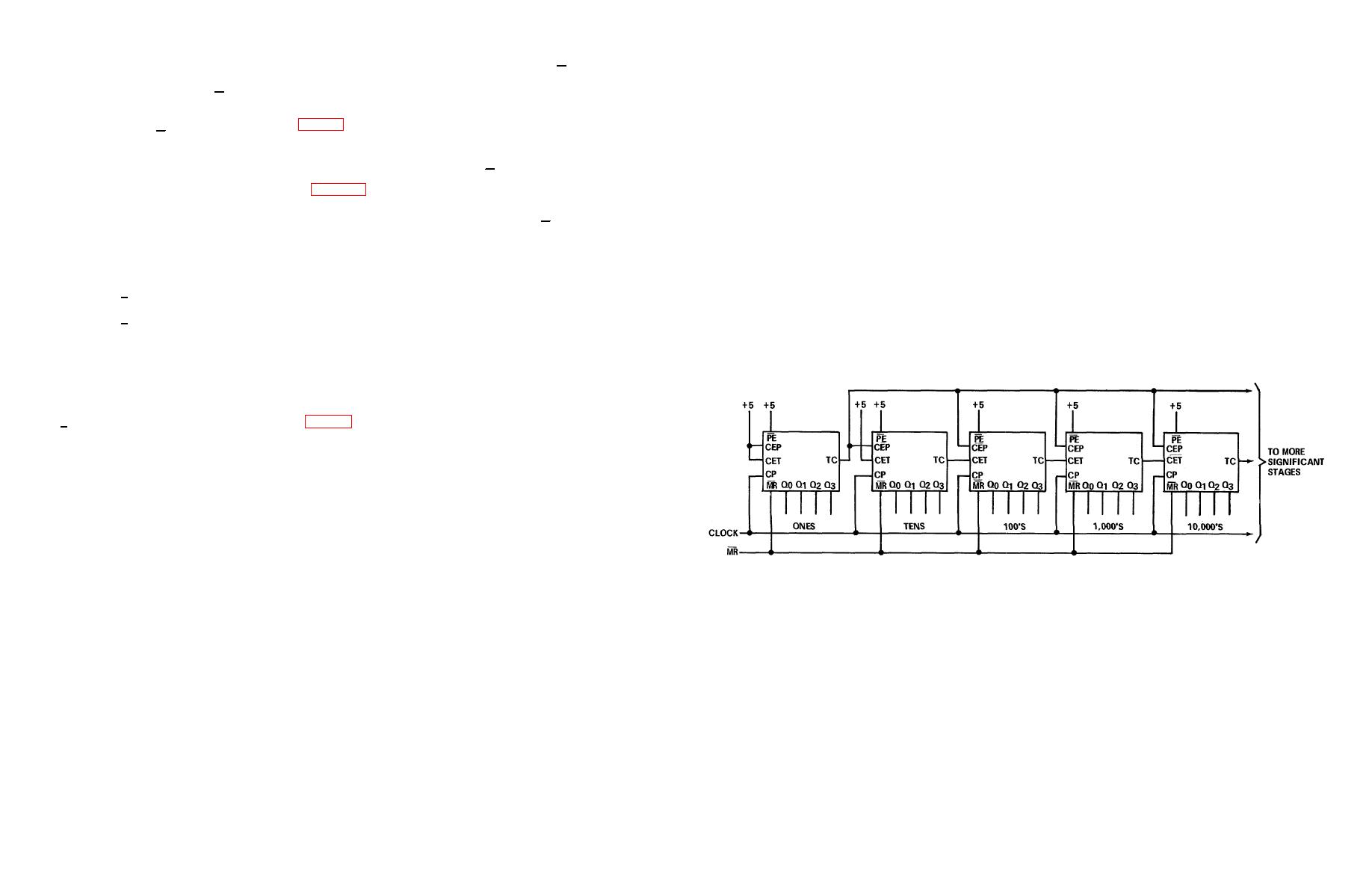

After the 10th clock pulse, the counter returns to zero state without applying a low to MR. Counters may be cascaded to

provide multistage synchronous counting, as shown in figure 3-24.

(e) The count enable inputs CEP (pin 7), and CET (pin 10) of the first counter are tied to +5 Vdc. Therefore, this

counter is continuously enabled, and counts as long as clock pulses are present and master reset MR (pin 1) is high. Note

that although the CP (pin 2) input of the second stage sees every one of the clock pulses, only one out of every 10 clock

pulses is enabled (at CEP) by the TC (pin 15) output of the first counter. Thus, the second counter advances by one count

for every 10 pulses of the clock. The remaining stages are enabled only if the following two conditions are met:

1.

The TC output (pin 15) of the first stage is high.

2.

The TC output of the state preceding the state under consideration is high.

(f) This creates an enable "window" one clock period wide for every high of the TC output of the preceding

stage. Therefore, the following stage advances by one count for every 10 counts of the preceding stage, which is the desired

mode of operation. The truth table for the second stage may be obtained from the truth table for the first stage by

substituting 10 through 100 for 1 through 10 in the first and last column. The truth table for the third stage may be obtained

from the truth table for the first stage by substituting 100 through 1000 for 1 through 10 in the first and last column, etc.

g. One-of-Ten Decoder. (MIS-18698/119-01) (fig. 3-25) This decoder accepts four active HIGH BCD inputs and

provides 10 mutually

Figure 3-24. Fast synchronous multistage counting

3-26